Laundry Analogy - PipeliningLet's say that there are four loads of dirty laundry that need to be washed, dried, and folded. Suppose the:

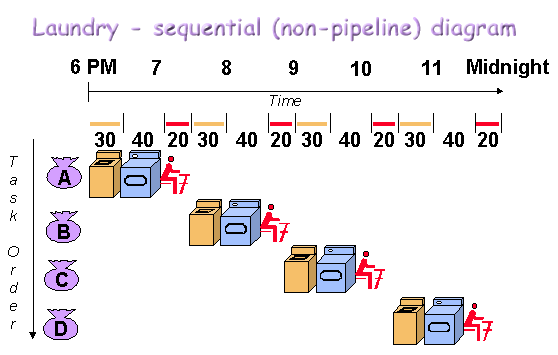

We could tackle the job sequentially - do the tasks in series. Start by putting the the first load in the washer for 30 minutes, then drying it for 40 minutes, and then taking 20 minutes to fold the clothes. We would then start on the second load. Pick up the second load and wash, dry, and fold, and repeat these actions in turn for the third and fourth loads. Suppose we started at 6 PM and worked as efficiently as possible, we would still be doing laundry until midnight!

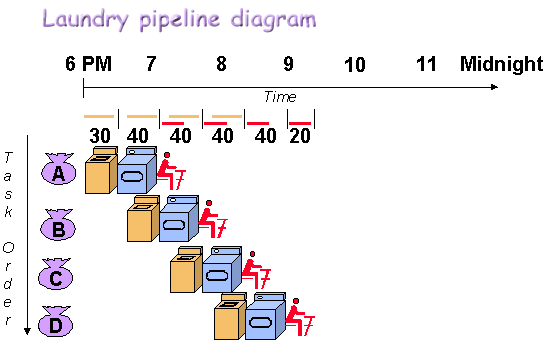

A smarter approach to the problem, however, would be to 'pipeline' the action - make efficient use of the machines available. We could put the second load of dirty laundry into the washer straight after the first wash load had finished and been put into the dryer. Then, while the first load was being folded, the second load would dry, and a third load could be added to the pipeline of laundry. Using this method, the laundry would be finished by 9:30.

While different CPUs have different numbers of steps, they are basically variations of these five datapath steps, used in the MIPS R3000 processor:

If you look at the laundry pipeline diagram, you'll notice that although the washer finishes in half an hour, the dryer takes an extra ten minutes, and so the wet clothes must wait ten minutes for the dryer to free up. Thus, the length of the pipeline is dependent on the length of the longest step. It is therefore most efficient to have small equally sized steps in processing so that efficient pipelining can be incorporated. Because RISC (Reduced Instruction Set Computing) instructions are simpler than those used in pre-RISC processors (now called CISC, or Complex Instruction Set Computer), they are more conducive to pipelining. While CISC instructions varied in length, RISC instructions are all the same length and can be fetched in a single operation. Ideally, each of the stages in a RISC processor pipeline should take 1 clock cycle so that the processor finishes an instruction each clock cycle and averages one cycle per instruction (CPI).

|

|

Custom Search