MIPS Architecture

MIPS was originally an acronym for:

MIPS was originally an acronym for:

Microprocessor without Interlocked Pipeline Stages.

(He even became a Super Mario character!)

It is the name for a set of microprocessors. A MIPS processor is a educed nstruction et omputer (RISC) Instruction Set Architecture (ISA) developed by MIPS Technologies (formerly MIPS Computer Systems, Inc.).

Early MIPS architectures were 32-bit, and later versions were 64-bit.

Multiple revisions of the MIPS instruction set exist - each revision allowing faster and more efficient transfer of instructions.

MIPS processors have their own dialect of assembly language that has specific instructions that relate to the architecture. The processors are so widespread that MIPS machine code dialect is the one that is commonly taught by Universities in their computer science courses.

See here for a MIPS tutorial

32-bit MIPS

Data Types

MIPS operates on:

- 32-bit (unsigned or 2's complement) integers,

- 32-bit (single precision floating point) real numbers,

- 64-bit (double precision floating point) real numbers;

- 32-bit words, bytes and half words can be loaded into general purpose registers (GPRs).

After loading into GPRs, bytes and half words are either zero or sign bit expanded to fill the 32 bits;

Only 32-bit units can be loaded into floating point registers (FPRs) and 32-bit are stored in .

64-bit real numbers are stored in two consecutive FPRs, starting with even-numbered register.

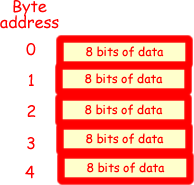

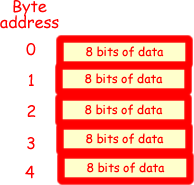

A byte = 8 bits

For 32-bit MIPS Processors:

Memory Organization

MIPS supports byte addressability - that means that a byte is the smallest unit with its own address.

Data is viewed as a large, single-dimension array, with a byte address. The memory address is an index into the array. "Byte addressing" means that the index points to a byte of memory.

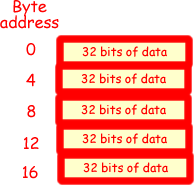

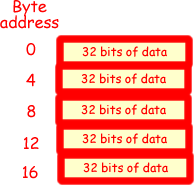

The 32-bit registers hold words of 32 bits.

a word = 32 bits = 4 bytes

232 bytes with byte addresses from 0 to 232-1

230 words with byte addresses 0, 4, 8, ... 230-4

An address is given as 32-bit unsigned integer;

MIPS restricts memory accesses to be aligned as follows:

A 32-bit word in a MIPS processor has to start at byte address that is multiple of 4. That means that a 32-bit word at address 4n includes four bytes with addresses:

4n, 4n+1, 4n+2, and 4n+3.

A 16-bit half word has to start at byte address that is multiple of 2; So, 16-bit word at address 2n includes two bytes with addresses:

2n and 2n+1.

MIPS Instruction Classes

- Instructions that move data:

- load to register from memory,

- store from register to memory,

- move between registers in same and different coprocessors

- ALU integer instructions:

register – register and registerimmediate computational instructions,

- Floating point instructions: register – register computational instructions and real number to/from integer conversion instructions,

- Control-related instructions,

- Special control-related instructions.

MIPS was originally an acronym for:

MIPS was originally an acronym for: