ISA

ISA (Industry Standard Architecture) is a very important abstraction layer in computer hardware. An abstraction layer is a way of hiding the implementation details of a particular set of functionality - you don't need to know how it works - just use it!

ISA links hardware and software in that it determines the speed with which software actions can occur and how information can be stored and accessed.

Synchronous Digital Systems are systems that operate in time with a clock pulse. There are two basic types of circuits synchronous digital systems:

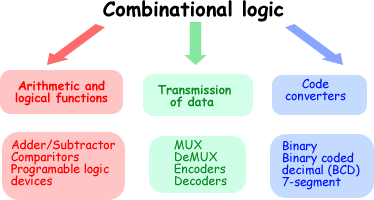

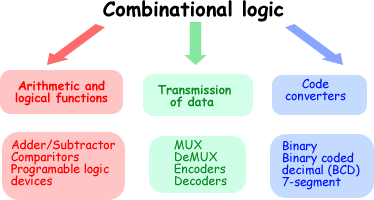

Stateless Combinational Logic circuits (e.g., data multiplexers - MUX, arithmetic/logic units, adder/subtractor circuits.)

Combinational Logic (CL) circuits is the general term for blocks of digital logic which contain no kind of memory. They can be considered as "decision making circuits". The relationship between the inputs and outputs is specified by the truth table and output is a function of the inputs only.

Combinational logic circuits are made up from individual logic gates. They combine logic gates together to process two or more signals in order to produce at least one output signal according to the logical function of the logic gate combination.

State circuits (e.g., registers)

These are circuits that store information.

The function of state elements

- Serve as a place to store values for some indeterminate amount of time:

- To help control the flow of information between combinational logic blocks.

To understand and analyse logic circuits you need to know how to use boolean algebra, write out truth tables, simplify logic expressions and logic gate diagrams.

Pipelining and ISA Design

The MIPS Instruction Set is designed for pipelining.

- All instructions are 32-bits.

easier to fetch and decode in one cycle .

x86: 1 to 17 byte instructions (x86 hardware actually translates to internal RISC instructions!) .

- Few and regular instruction formats

2 source register fields always in same place.

Can decode and read registers in one step.

- Memory operands only in Loads and Stores

Can calculate address 3rd stage, access memory 4th stage .

- Alignment of memory operands.

Memory access takes only one cycle

For more details on the MIPS processor see here.